TSMC announces a handful of 3nm system nodes, N2 coming in 2025

[ad_1]

TSMC announces a handful of 3nm system nodes, N2 coming in 2025

[ad_1]

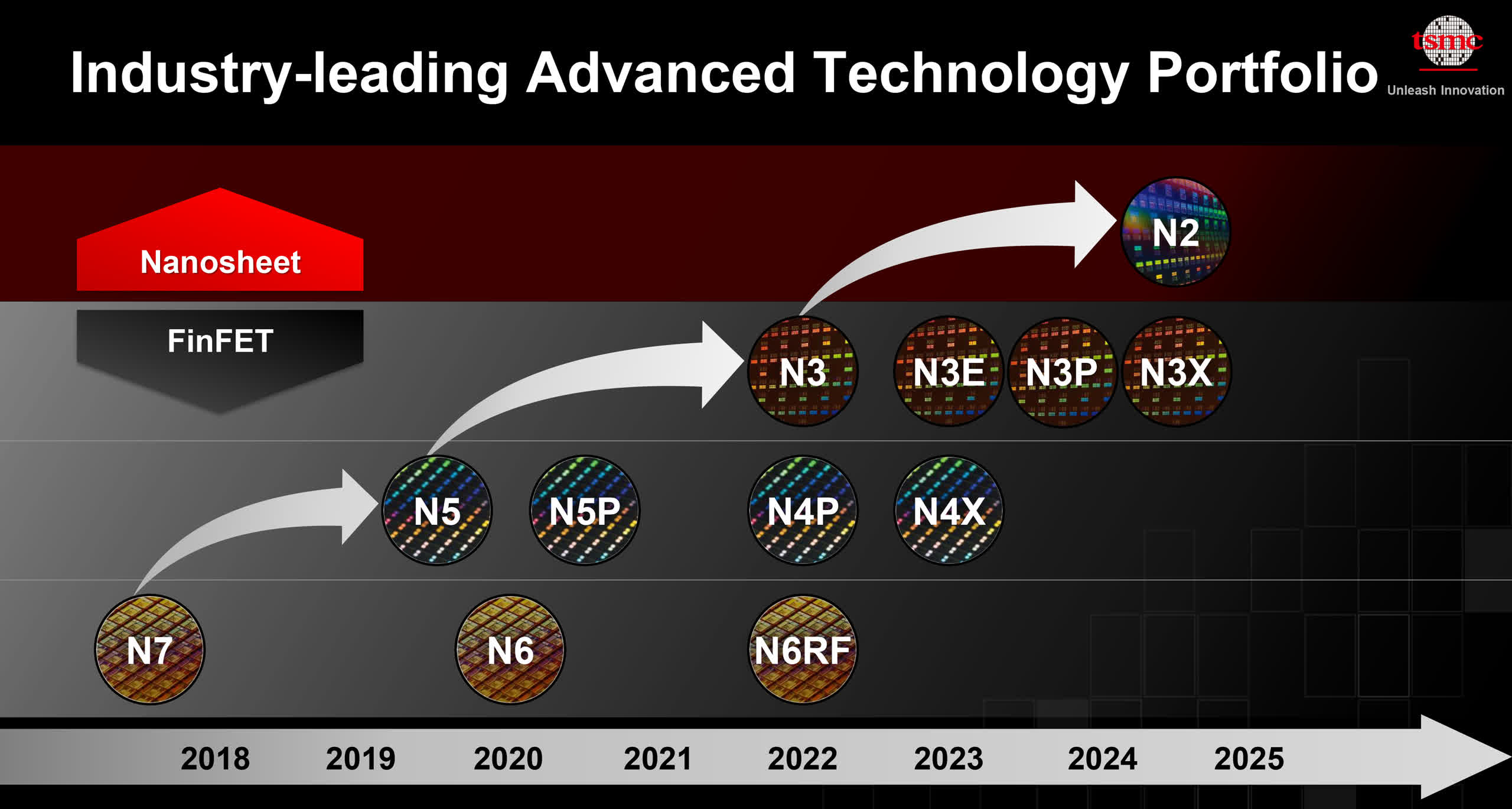

In a nutshell: TSMC has just declared its total lineup of 3nm class nodes launching more than the subsequent a few a long time. Its new FinFlex tech will give chip designers even more versatility to improve every common mobile for the wanted ability use, performance, and density.

TSMC has just unveiled its complete N3 household of approach nodes. Chip designers these as AMD, Apple, Nvidia, and even Intel will use these nodes more than the next couple yrs to fabricate their bleeding-edge chips.

The Taiwanese business has a full of 5 unique 3nm course nodes. N3 will start off large-quantity manufacturing later this calendar year, with the initial chips predicted to arrive at customers early subsequent calendar year. N3E will launch later on with general performance and effectiveness advancements, bigger yields, but slightly decreased logic density.

About 2024, TSMC will bring out N3P, which focuses on functionality improvements. N3S, which was not highlighted in TSMC's roadmap, was only briefly described in conversation by SVP Kevin Zhang.

Ultimately, N3X will occur out about a calendar year later on and allow for really high general performance at better voltages, with efficiency and costs taking the back again seat. This technique is identical to the 5nm class N4X process starting quantity producing up coming 12 months.

TSMC's N3 and N3E nodes will also assist the firm's new FinFlex tech. At present, chip designers have to decide 1 library for each block in just an SoC. With FinFlex, they is not going to have this limitation and will be capable to blend and match various libraries inside of each and every block.

They can use 2-1 (double-gate one-fin) FinFETs in some pieces in buy to reduce electric power usage and die measurement (value) and decide for 3-2 FinFETs in other areas in which greatest overall performance is paramount. In the meantime, 2-2 FinFETs supply a equilibrium of measurement, functionality, and electrical power usage.

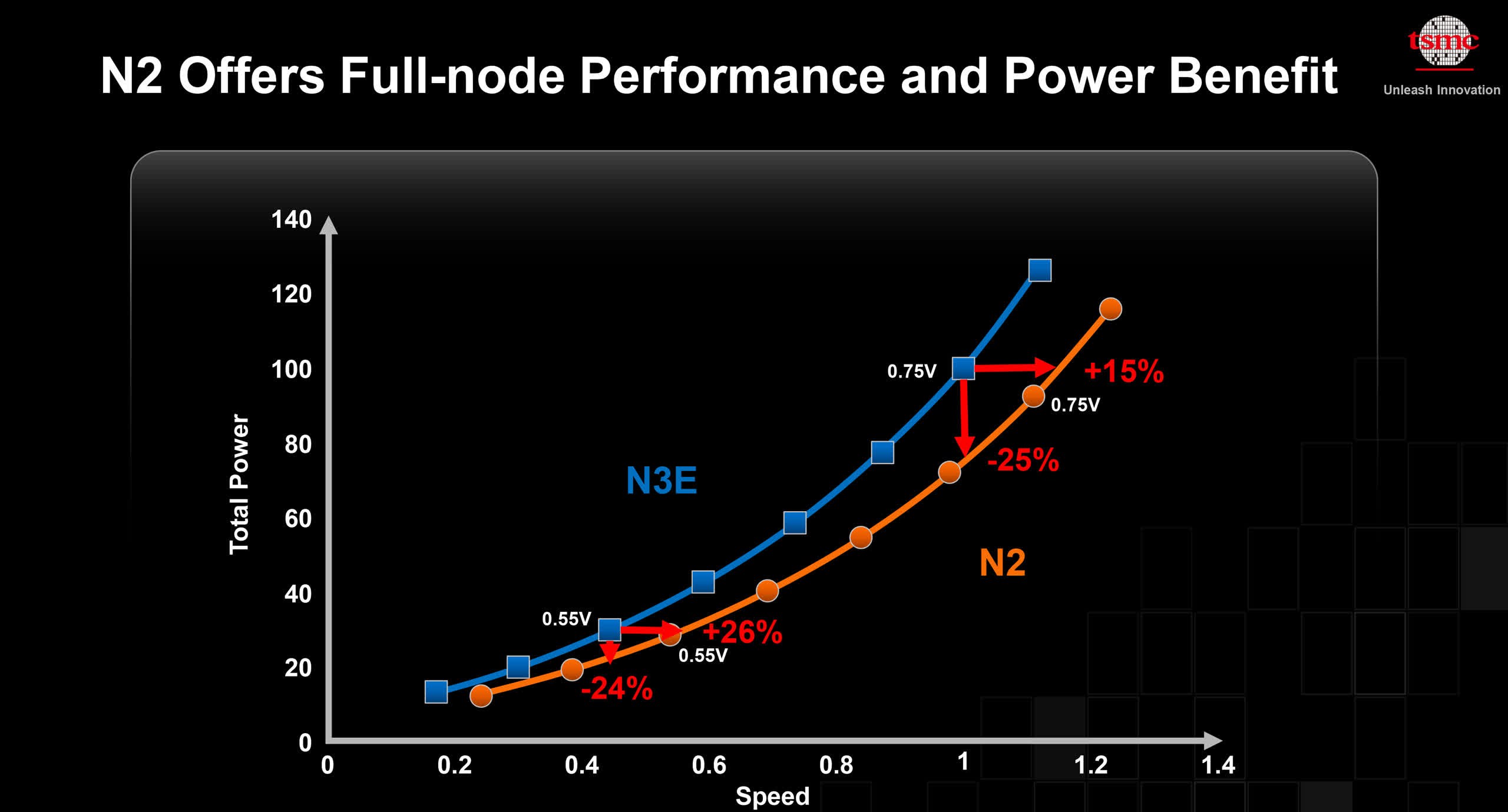

TSMC also described its forthcoming N2 course of action node, which will use gate-all-about field-impact transistors (GAAFETs), with strategies to commence volume producing in the next 50 percent of 2025.

As opposed to N3E, it will reportedly attract 25-30 p.c considerably less energy at the identical frequency and enable for 10-15 percent more functionality with the very same electricity usage and transistor depend. Meanwhile, chip density will reportedly enhance by in excess of 10 percent.

[ad_2]

0 comments:

Post a Comment